重大共性工艺-铜互连共性工艺

在集成電(diàn)路的工艺中,通过互连将器件连接从而形成電(diàn)路。随着摩尔定律的发展,互连从起初的简单的单层互连结构发展到多(duō)层互连结构,其中互连金属和材料、互连集成工艺也发生了巨大的变化。在目前主流的65nm及以下工艺中,由于互连延迟占据整个電(diàn)路的延迟中所占据的比例越来越大,需要采用(yòng)金属铜和低介電(diàn)材料。传统的介電(diàn)材料是二氧化硅,介電(diàn)常数(k)在3.9左右。通过在SiO2引入Si-F,Si-C键等弱极化健从而形成氟掺杂二氧化硅(k~3.7),碳掺杂二氧化硅(k~ 2.7)等,通过在碳掺杂二氧化硅中进一步引入微孔等能(néng)够继续降低介電(diàn)常数到2.55左右。通过空气隙可(kě)以实现介電(diàn)常数下降20%左右,这样介電(diàn)常数可(kě)以下降到2以下。

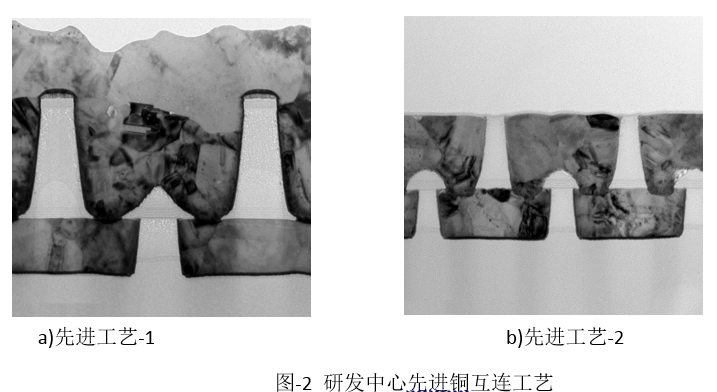

现有(yǒu)的铜互连的集成工艺是先在介质上形成沟槽,然后进行金属的淀积和金属的CMP。集成主要工艺工艺步骤见图-1:首先是介质的淀积见图-1a;此步通常是采用(yòng)PECVD的方式进行低介電(diàn)材料的淀积,如果是k為(wèi)2.5左右的材料还需要进行UV 处理(lǐ)。2然后是光刻工艺,进行涂胶曝光显影,形成特征尺寸;(图-1b);3.是介质的刻蚀工艺,采用(yòng)All in One的一步刻蚀同时现场沟槽和通孔,然后是清洗过程(图-1c);4. 后续是阻挡层和籽晶层的淀积(图-1d),阻挡层由TaN/Ta两层材料组成,其中TaN可(kě)以防止铜的扩散,籽晶层是铜Ta,这一步通常采用(yòng)PVD的淀积方式。5是铜的電(diàn)镀工艺(图-1e),為(wèi)了实现无缝電(diàn)镀,在镀液中将加入多(duō)种化學(xué)成分(fēn),如加速剂、平整剂、抑制剂等。6是铜的CMP(化學(xué)机械研磨)过程(图-1f),在镀铜工艺后,采用(yòng)CMP的方式去除多(duō)余的铜。CMP工艺是采用(yòng)研磨液进行的平坦化工艺。

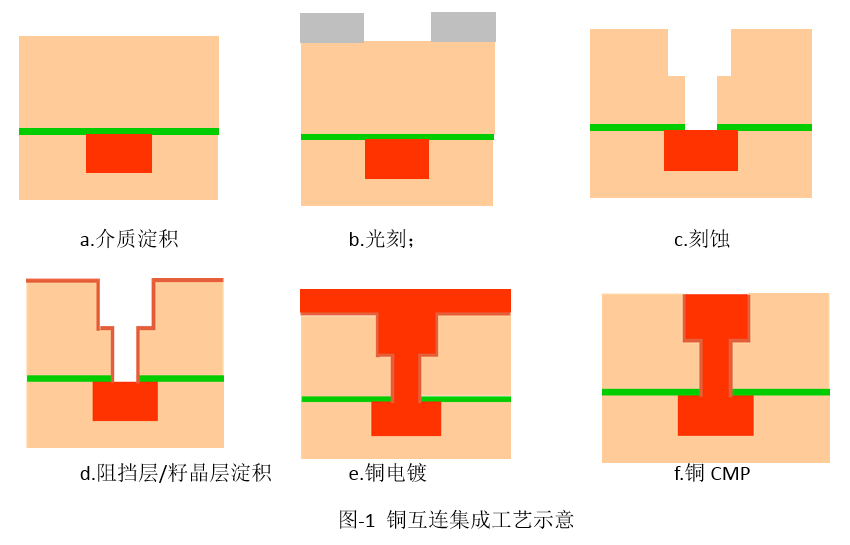

研发中心基于自有(yǒu)的铜互连设备已开发了55nm至28 nm相关工艺,包括介质刻蚀、阻挡层/籽晶层淀积、铜電(diàn)镀等,并实现了铜互连工艺集成(图-2)。